In our latest video, we demonstrate how to analyze complex nonlinear RF and Microwave circuits using the Harmonic Balance (HB) analysis method.

Introduction to Harmonic Balance (HB)

In TINA v16 and later versions, you can analyze complex nonlinear RF and Microwave circuits using the Harmonic Balance (HB) analysis method. This approach is crucial for high-frequency design.

- The HB Advantage: The key benefit of this method is that it does not require detailed time-domain simulation, which can be computationally prohibitive for GHz-range signals. Instead, you only need to specify the desired base harmonics, and the program calculates and displays the resulting spectrum lines in the frequency domain.

- Locating Examples: Example circuits for Harmonic Balance analysis can be found in the

Examples\RF\HBfolder within TINA.

Let’s explore a few practical examples.

1: Frequency Tripler Circuit

We begin with a classic nonlinear application: frequency multiplication.

Example Circuit: Tripler BJT.TSC (located in Examples\RF\HB)

Circuit Description

This frequency tripler circuit generates a 2.4 GHz output signal, which is exactly three times the 800 MHz input frequency. It achieves this using a high-frequency bipolar transistor (MMBR941) as the nonlinear element.

Running the Analysis

- To obtain the output spectrum, run Harmonic Balance Analysis from the

Analysismenu using the appropriate settings. - Ensure that Vout is selected in the Output field.

Analysis Results

The results clearly demonstrate the tripling effect:

- The dominant spectral component appears at the third harmonic (2.4 GHz) with an amplitude of 113.85 mV.

- The fundamental component at 800 MHz is significantly suppressed, measured at only 1.77 mV.

This confirms the correct frequency-tripling operation.

You can view the spectrum lines graphically by clicking the Draw button in the Harmonic Balance Analysis dialog. To display the numeric values of the spectrum lines, click the (Auto Label) button on the diagram, and then click the top of any spectrum line.

2: AM Demodulator and Direct Frequency Specification

A major feature of the Harmonic Balance analysis is the ability to specify the desired spectrum lines directly by listing their frequencies. This is particularly useful when analyzing signals that have widely separated frequency components.

Example Circuit: AM Demodulator with PIN Diode.TSC

Circuit Description

This circuit is a simple PIN diode detector used for demodulating an Amplitude Modulated (AM) signal. It includes an RC low-pass filter at its output to retrieve the modulating signal.

The input AM signal is modeled using three generators:

- One at the 1 GHz carrier frequency.

- Two generators forming the upper and lower sidebands, each spaced 100 kHz from the carrier.

Why Direct Specification is Necessary

The goal is to calculate the amplitude of the 100 kHz modulating signal at the output using HB analysis.

- If we tried to define the sidebands and the carrier as multiples of the low 100 kHz base frequency, we would require the calculation of over 10,000 spectrum lines, which is impractical.

- The Solution: We specify only the three known input frequencies (the carrier and the two sidebands) directly in the HB Analysis dialog.

After calculation, the values of the spectral voltages appear, including the critical low-frequency demodulated component.

Verification using Time-Domain and Fourier Analysis

Although the HB analysis provides the frequency spectrum, the results can be cross-checked using time-domain methods.

- Transient Analysis: Select Transient from the

Analysismenu. The waveform of the high-frequency AM signal and the low-frequency demodulated signal will appear in the diagram window. - Fourier Series Analysis: To perform a Fourier check, click the upper demodulated signal and select Fourier… from the

Processmenu.- Ensure the Base frequency is set to 100 kHz.

- Fourier Result: 208.75 mV at 100 kHz.

- HB Result: 202.70 mV at 100 kHz.

The excellent agreement between the two methods confirms the accuracy of the Harmonic Balance calculation.

Conclusion

The Harmonic Balance method provides a robust and computationally efficient way to analyze nonlinear RF and microwave circuits, especially when dealing with widely separated frequency components.

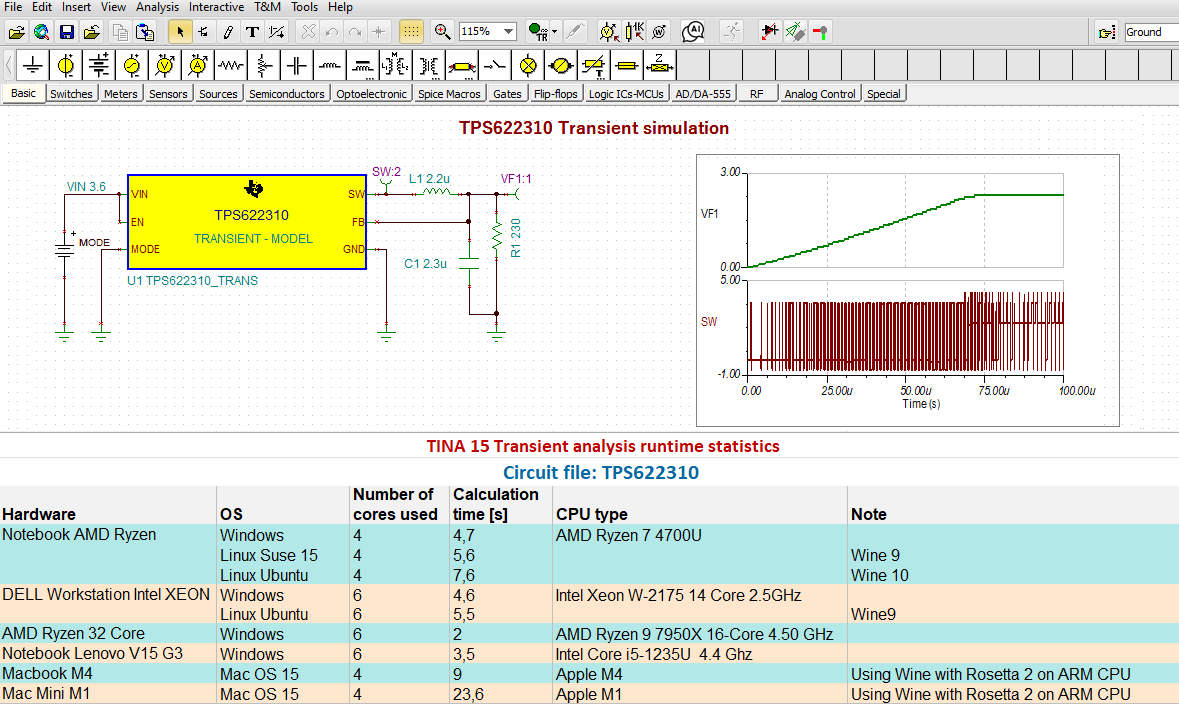

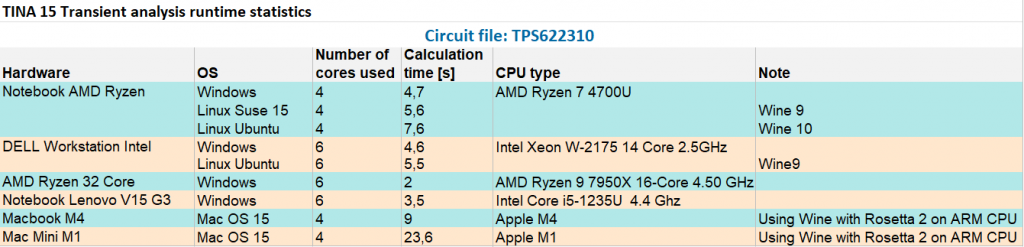

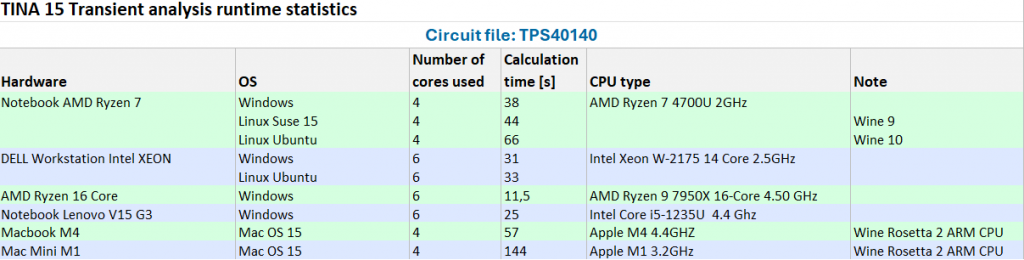

However, as evidenced by the verification step, the growing performance of modern computers is making time-domain methods (like Transient Analysis coupled with Fourier analysis) increasingly competitive and useful for validating the results obtained from the Harmonic Balance technique.