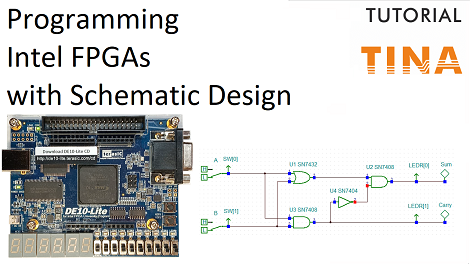

In this tutorial video, we will show you how to create a digital circuit and download it to a Terasic DE10-Lite FPGA board using TINA’s Schematic Editor.

In a similar way it is also possible to download digital circuits to the FPGA of DesignSoft’s LabXplorer.

We will use a free Intel tool, Quartus Prime Lite Edition, which is required for the Intel MAX 10 FPGA in the Terasic DE10-Lite board.

For other Intel FPGAs, you might need to use the Standard or Pro Edition of Quartus.

We presume that the board is accessible from your machine and that the necessary drivers have been installed.

As demonstration we use a half adder circuit which you can find in the Example folder of TINA.

Before testing our circuit in a real FPGA development board environment, we need to extend our schematic with FPGA Pin connectors. We add 2 Pin connectors to the inputs and 2 Pins to the outputs.

Next, we rename the FPGA input and output Pins (including their labels) accordingly as those on the FPGA boards.

After that, we present how to generate the source file for Intel Quartus Lite.

TINA always creates a VHD file from any type of representation of the digital circuit.

That is, schematic diagrams, VHDL, Verilog codes or combinations thereof are always translated into a VHD file for Quartus.

The QSF—Quartus Prime Settings— file guides the FPGA software for which the physical pins on the FPGA will be the inputs and outputs. The qsf is made from the FPGA pin settings we made previously.

To produce downloadable content, we first have to create the Quartus Prime Lite project.

Testing the simulated Half Adder circuit along with the programmed DE10-Lite hardware.

As soon as we finish programming the hardware we can start testing our simulated Half Adder circuit and see how it works along with the programmed DE10-Lite hardware.

We will change the virtual switches in TINA by clicking them on the screen, and at the same time we will also change the real switches on the DE10-Lite board.

- If both inputs are low, then Sum and Carry are also low.

- If just one input is high, then Sum is high and Carry is low.

- If both inputs are high, then Sum is low and Carry is high.

As you can see, in all cases the results are exactly the same.

This is a great example of demonstrating the power of simulation since you can test and debug circuits even before realizing them, and in our case before downloading to FPGA, where if there were any issues it would be extremely hard to find the problem.

To watch our tutorial and learn more please click here.

You can learn more about TINA here: www.tina.com

You can learn more about TINACloud here: www.tinacloud.com