SystemC SIMULATION

SystemC SIMULATION

- Verilog-A & AMS Simulation

- SystemVerilog Simulation

- Verilog Simulation

- VHDL Simulation

- VHDL-AMS Simulation

SystemC is another great tool for modeling hardware. It includes all the features of C++, used all over the world, and a C++ class library specially designed for system design. SystemC has an open-source free implementation and you can compile it into a very efficient executable binary code with the also free Visual Studio Community C++ compiler of Microsoft. In SystemC you can model hardware at a higher abstraction level than in other HDLs and so for modeling some very complex hardware e.g. microcontrollers it is more easy and efficient to use than other HDLs like VHDL or Verilog.

In v11 and later versions of TINA you can also create and use components modeled in SystemC both in TINA and TINACloud. The following are the requirements to use SystemC with TINA.

Low-pass filter example

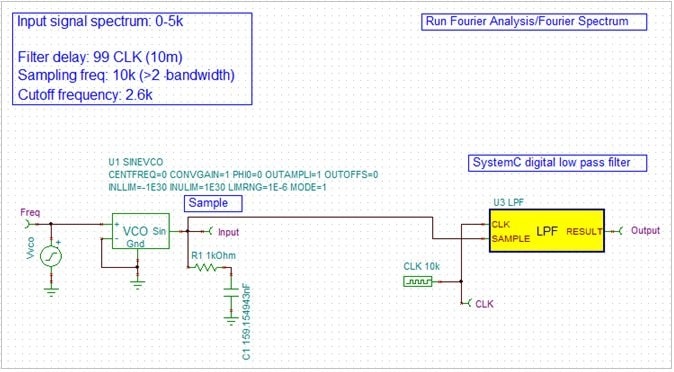

Open the ExamplesSystemCsc lpf.TSC example.

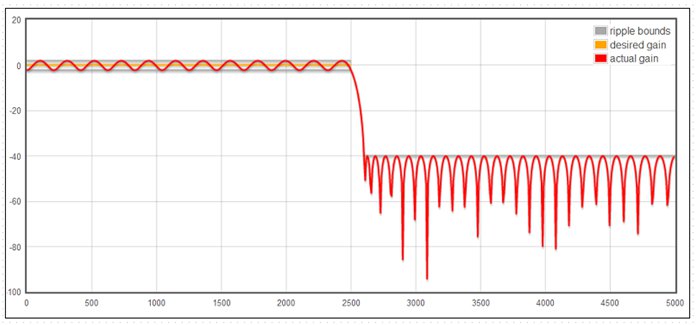

The filter characteristics and C-code is designed by the free tool at

http://t-filter.engineerjs.com/

The generated C-code was placed in the fir.cpp file.

Run Analysis/Fourier Analysis/Fourier Spectrum…

Press the

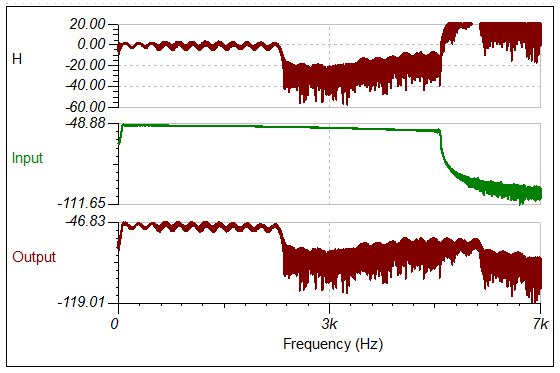

Press the More button. Type Output(s)/Input(s) in the Line Edit. Type H in the new function name. Press Create. Press OK. Select View/ Separate curves.

The result is the following

The most important part of the SystemC macro:

void fir::proc()

{

double u, y;

if (CLK.read() == SC_LOGIC_1) {

sc_logic sc_val;

// CALC

x[0] = SAMPLE; y = 0;

for (int k=0; k < M; k++){

y += b[k]*x[k];

}

// SHIFT

for (int k=M-1; k>=1; k—)

x[k] = x[k-1];

// SET VALUE

RESULT = y;

n++;

}

}

You can find this example in the Examples/Fir folder of the systemc_model.zip.